Homemade Spi Flash Programmer Software Download For Mac

- Homemade Spi Flash Programmer Software Download For Mac Windows 10

- Homemade Spi Flash Programmer Software Download For Mac Os

- Homemade Spi Flash Programmer Software Download For Mac Download

- Homemade Spi Flash Programmer Software Download For Mac Windows 7

- NodeMCU flasher is a firmware programmer for NodeMCU DEVKIT V0.9. You can use it to program NodeMCU DEVKIT or your own ESP8266 board. You MUST set GPIO0 to LOW before programming, and NodeMCU DEVKIT V0.9 will do it automatically.

- Now I got my hands on STM32 based programmer for SPI chips (SOP8-SOP16, see pics below). However this programmer seems to work only with software provided by whoever designed it, which is only available on Windows XP (attempting to run it on Win7 results in it working, but machine complains about libusb drivers that it installs).

- SPI Flash Programming Solution. SF100 SPI NOR Flash Programmer; SF600 SPI NOR Flash Programmer; SF600Plus SPI NOR Flash Programmer; SF700 SPI Flash Programmer; EM100Pro-G2 SPI NOR Flash Emulator; SF100 ISP Evaluation Kit; SPI NOR Flash Development Kit (SF100) SPI NOR Flash Development Kit (SF600).

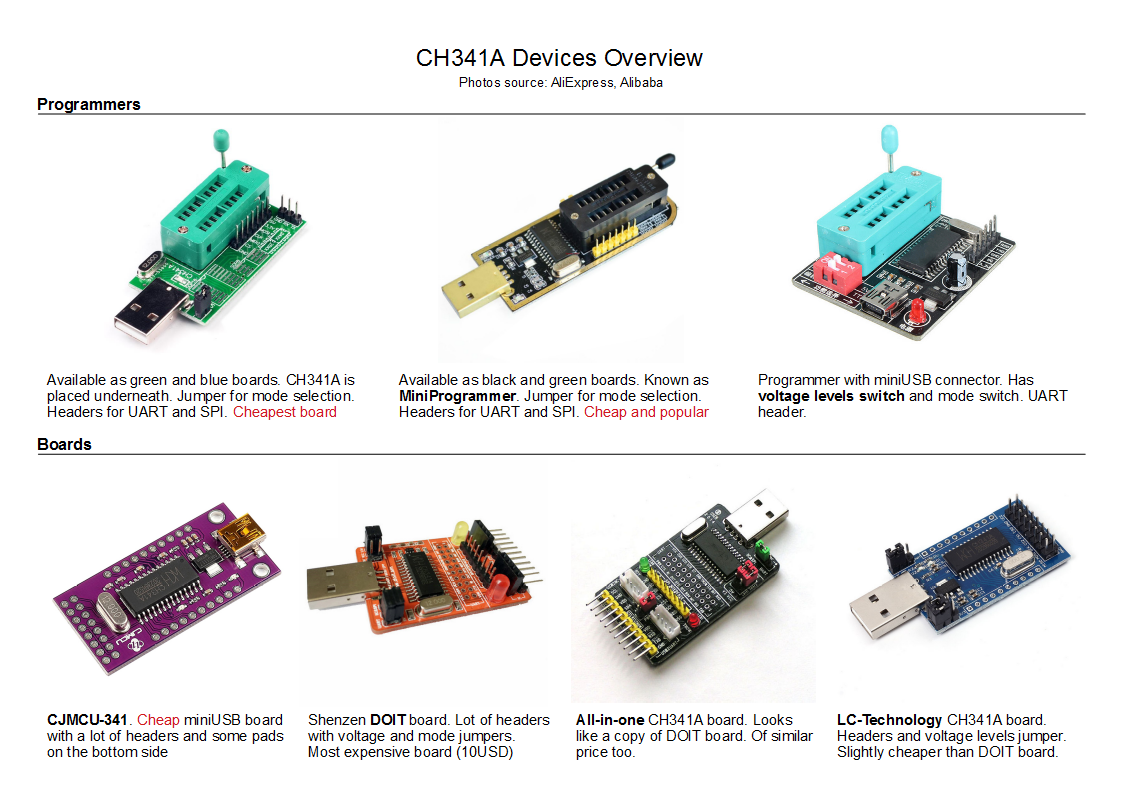

- Support 24 EEPROM and 25 SPI flash 8pin or 16pin chip. 1x CH341A 24 25 Series EEPROM Flash BIOS USB Programmer. CH341Linux+MAC+Android+PDF: Driver&Document.

This is usually done with SPI chips only. Some mainboards have a special header for this (often named 'ISP', 'ISP1', or 'SPI') and there should be no problem with accessing the chip then as long as the wires are not too long. If there is no special header then using a special SO(IC) clip is an easy and reliable way to attach an external programmer. Python3 spiflashprogrammerclient.py -f wr703n.orig.bin -flash-offset 16711680 -file-offset 4128768 verify Solder the new chip in. If you try this, let me know!

J-Flash SPI is a PC software running on Microsoft Windows (backward compatible down to Windows 2000) systems, Linux or macOS, which allows direct programming of SPI flashes via J-Link or Flasher. The flash is programmed directly via J-Link using the SPI protocol, no CPU / MCU in between.

- Direct programming of SPI flash via J-Link (no CPU / MCU in between)

- Since J-Link communicates directly with the flash, even flashes connected to CPUs not supported by J-Link can be programmed

- Cross-platform (GUI and command line version available for Windows, Linux and macOS)

- Auto-detection of popular SPI flashes

- Any SPI flash can be supported. All flash parameters can be manually configured/overridden, if required

- Can be controlled via command-line

- Part of the J-Link software and documentation package

- 1.J-Flash SPI - programming tool for SPI flash memories that simply works!

- 2.Licensing

- 3.20-pin connection

- 4.20-pin QSPI connection

- 5.J-Link 10-Pin Needle Adapter Connection

- 6.Which SPI flash devices are supported?

- 6.1.Atmel / Adesto DataFlash

- 7.Evaluation hardware

- 8.Command line version

- 9.Flash Programming Speed

- 10.FAQ

J-Flash SPI - programming tool for SPI flash memories that simply works!

J-Flash SPI is a PC software running on Microsoft Windows (backward compatible down to Windows 2000) systems, Linux or macOS, which allows direct programming of SPI flashes via J-Link or Flasher. The flash is programmed directly via J-Link using the SPI protocol, no CPU / MCU in between.

Most common SPI flashes are automatically recognized by their respective ID and can easily be programmed with no further setup / configuration of J-Flash SPI needed to be done by the user.

In order to use J-Flash SPI, either a higher-end J-Link model (J-Link PLUS or higher, click here for the debug probe model overview) or a Flasher Production Programmer (click here for the flash programmer model overview) is needed.

20-pin connection

The following table lists the pinout for the SPI interface on J-Link / Flasher.

| Pin | Signal | Type | Description |

|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. |

| 2 | Not connected | NC | Leave open on target side. |

| 3 | Not connected | NC | Leave open on target side. |

| 5 | DI | Output | Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI. |

| 7 | nCS | Output | Chip-select of target SPI (active LOW). |

| 9 | CLK | Output | SPI clock signal. |

| 11 | Not connected | NC | Leave open on target side. |

| 13 | DO | Input | Data-out of target SPI. Input of J-Link, used to receive data from the target SPI. |

| 15 | nRESET | Output | Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

| 17 | Not connected | NC | Leave open on target side. |

| 19 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

Pins 4, 6, 8, 10, 12 are GND pins connected to GND in J-Link. They should also be connected to GND in the target system.

*On later J-Link products like the J-Link ULTRA, these pins are reserved for firmware extension purposes. They can be left open or connected to GND.

Pinout SPI 20-pin

The following table lists the pinout for the quad SPI (QSPI) interface.

| Pin | Signal | Type | Description | |||

|---|---|---|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. | |||

| 2 | Not connected | NC | Leave open on target side. | |||

| 3 | IO1 | I/O | Bi-directional data I/O pin 1 | |||

| 5 | IO0/DI | I/O | Single:>7 | nCS | Output | Chip-select of target SPI (active LOW). |

| 9 | CLK | Output | SPI clock signal. | |||

| 11 | IO2 | I/O | Bi-directional data I/O pin 2 | |||

| 13 | DO | Input | Single:>15 | nRESET | Output | Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

| 17 | IO3 | I/O | Bi-directional data I/O pin 3 | |||

| 19 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

Pins 4, 6, 8, 10, 12 are GND pins connected to GND in J-Link. They should also be connected to GND in the target system.

*On later J-Link products like the J-Link ULTRA, these pins are reserved for firmware extension purposes. They can be left open or connected to GND.

Pinout QSPI 20-pin

J-Link 10-Pin Needle Adapter Connection

The following table lists the pinout for the SPI interface on J-Link / Flasher when using the J-Link 10-pin Needle Adapter (model 8.06.04).

| Pin | Signal | Type | Description |

|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. |

| 2 | nCS | Output | Chip-select of target SPI (active LOW). |

| 4 | CLK | Output | SPI clock signal. |

| 5 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

| 6 | DO | Input | Data-out of target SPI. Input of J-Link, used to receive data from the target SPI. |

| 7 | Not connected | NC | Leave open on target side. |

| 8 | DI | Output | Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI. |

| 9 | Not connected | NC | Leave open on target side. |

| 10 | nRESET | Output | Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

Pin 3 is GND pin connected to GND in J-Link. It should also be connected to GND in the target system.

Notes regarding nRESET: If there is another device / peripheral that also controls the SPI flash (e.g. a CPU the flash is connected to), nRESET of J-Link should be connected to the reset of the target system or the reset pin of the CPU to make sure that J-Link can keep the CPU in reset while programming the SPI flash.

J-Flash SPI connection

J-Flash SPI is able to auto-detect common SPI flashes automatically, via their respective ID. Anyhow, since all flash parameters (size, commands etc.) can also be manually configured by the user, any SPI flash device can be supported. The list of flash devices that are supported by the flash auto-detection of J-Flash SPI can be found here:

Atmel / Adesto DataFlash

Atmel DataFlash is not supported by J-Flash SPI as its instruction set and handling in general is significantly different from any other SPI flash. Moreover, its page/sector size is not a power of 2, making it incompatible to existing concepts.

Selecting the right (Q)SPI flash that fits the needs can be a difficult task. There are plenty of different flashes as well as vendors available and creating a hardware for each candidate is time consuming and costly.

To make evaluation of different (Q)SPI flashes a lot easier, we have created a (QSPI) evaluation board.

Command line version

A command line version of J-Flash SPI is available for Windows, Linux and macOS, too. The command line version is also part of the J-Link software and documentation package. Please note that the GUI version of J-Flash SPI can also be controlled from the command line.

Due to the high performance and the efficient protocol of J-Link/Flasher, programming speeds up to the max. flash programming specified by the flash vendor, can be achieved.

| Flash device | Programming speed1 |

|---|---|

| ISSI IS25LP128 | 500 KB/s |

| ISSI IS25LD040 | 100 KB/s |

| ISSI IS25LQ080 | 340 KB/s |

| ISSI IS25CD010 | 100 KB/s |

| ISSI IS25CQ032 | 190 KB/s |

| Macronix MX25L3235E | 285 KB/s |

| Macronix MX66L1G45G | 430 KB/s |

| Macronix MX66L51235F | 315 KB/s |

| Micron N25Q128A | 270 KB/s |

| Micron M25P10 | 160 KB/s |

| Micron M25PX16 | 230 KB/s |

| Micron M45PE10 | 230 KB/s |

| Micron M25PE4 | 215 KB/s |

| Spansion S25FL128 | 410 KB/s |

| Spansion S25FL116K | 265 KB/s |

| Winbond W25Q128FV | 340 KB/s |

1 Max. flash programming speed that can be achieved depends on flash device. Flash programming is done in pages and page size as well as page programming time varies from device to device. For more information about the page programming time for a specific flash device, please refer to the appropriate datasheet.

FAQ

A: Please check the SEGGER wiki for more information which J-Link hardware versions support the 'SPI interface': wiki.segger.com/Software_and_Hardware_Features_Overview

More Information

Purchase

Technology

Accessories

Tools

Models

J-Flash SPI is a PC software running on Microsoft Windows (backward compatible down to Windows 2000) systems, Linux or macOS, which allows direct programming of SPI flashes via J-Link or Flasher. The flash is programmed directly via J-Link using the SPI protocol, no CPU / MCU in between.

- Direct programming of SPI flash via J-Link (no CPU / MCU in between)

- Since J-Link communicates directly with the flash, even flashes connected to CPUs not supported by J-Link can be programmed

- Cross-platform (GUI and command line version available for Windows, Linux and macOS)

- Auto-detection of popular SPI flashes

- Any SPI flash can be supported. All flash parameters can be manually configured/overridden, if required

- Can be controlled via command-line

- Part of the J-Link software and documentation package

- 1.J-Flash SPI - programming tool for SPI flash memories that simply works!

- 2.Licensing

- 3.20-pin connection

- 4.20-pin QSPI connection

- 5.J-Link 10-Pin Needle Adapter Connection

- 6.Which SPI flash devices are supported?

- 6.1.Atmel / Adesto DataFlash

- 7.Evaluation hardware

- 8.Command line version

- 9.Flash Programming Speed

- 10.FAQ

J-Flash SPI - programming tool for SPI flash memories that simply works!

J-Flash SPI is a PC software running on Microsoft Windows (backward compatible down to Windows 2000) systems, Linux or macOS, which allows direct programming of SPI flashes via J-Link or Flasher. The flash is programmed directly via J-Link using the SPI protocol, no CPU / MCU in between.

Most common SPI flashes are automatically recognized by their respective ID and can easily be programmed with no further setup / configuration of J-Flash SPI needed to be done by the user.

In order to use J-Flash SPI, either a higher-end J-Link model (J-Link PLUS or higher, click here for the debug probe model overview) or a Flasher Production Programmer (click here for the flash programmer model overview) is needed.

20-pin connection

The following table lists the pinout for the SPI interface on J-Link / Flasher.

| Pin | Signal | Type | Description |

|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. |

| 2 | Not connected | NC | Leave open on target side. |

| 3 | Not connected | NC | Leave open on target side. |

| 5 | DI | Output | Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI. |

| 7 | nCS | Output | Chip-select of target SPI (active LOW). |

| 9 | CLK | Output | SPI clock signal. |

| 11 | Not connected | NC | Leave open on target side. |

| 13 | DO | Input | Data-out of target SPI. Input of J-Link, used to receive data from the target SPI. |

| 15 | nRESET | Output | Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

| 17 | Not connected | NC | Leave open on target side. |

| 19 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

Pins 4, 6, 8, 10, 12 are GND pins connected to GND in J-Link. They should also be connected to GND in the target system.

*On later J-Link products like the J-Link ULTRA, these pins are reserved for firmware extension purposes. They can be left open or connected to GND.

Pinout SPI 20-pin

The following table lists the pinout for the quad SPI (QSPI) interface.

| Pin | Signal | Type | Description | |||

|---|---|---|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. | |||

| 2 | Not connected | NC | Leave open on target side. | |||

| 3 | IO1 | I/O | Bi-directional data I/O pin 1 | |||

| 5 | IO0/DI | I/O | Single:>7 | nCS | Output | Chip-select of target SPI (active LOW). |

| 9 | CLK | Output | SPI clock signal. | |||

| 11 | IO2 | I/O | Bi-directional data I/O pin 2 | |||

| 13 | DO | Input | Single:>15 | nRESET | Output | Target CPU reset signal (active LOW). Typically connected to the reset pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

| 17 | IO3 | I/O | Bi-directional data I/O pin 3 | |||

| 19 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

Pins 4, 6, 8, 10, 12 are GND pins connected to GND in J-Link. They should also be connected to GND in the target system.

*On later J-Link products like the J-Link ULTRA, these pins are reserved for firmware extension purposes. They can be left open or connected to GND.

Pinout QSPI 20-pin

J-Link 10-Pin Needle Adapter Connection

The following table lists the pinout for the SPI interface on J-Link / Flasher when using the J-Link 10-pin Needle Adapter (model 8.06.04).

| Pin | Signal | Type | Description |

|---|---|---|---|

| 1 | VTref | Input | This is the target reference voltage. It is used to check if the target has power, to create the logic-level reference for the input comparators and to control the output logic levels to the target. It is normally fed from Vdd of the target board and must not have a series resistor. |

| 2 | nCS | Output | Chip-select of target SPI (active LOW). |

| 4 | CLK | Output | SPI clock signal. |

| 5 | 5V-Supply | Output | This pin can be used to supply power to the target hardware. Older J-Links may not be able to supply power on this pin. |

| 6 | DO | Input | Data-out of target SPI. Input of J-Link, used to receive data from the target SPI. |

| 7 | Not connected | NC | Leave open on target side. |

| 8 | DI | Output | Data-input of target SPI. Output of J-Link, used to transmit data to the target SPI. |

| 9 | Not connected | NC | Leave open on target side. |

| 10 | nRESET | Output | Target CPU reset signal. Typically connected to the RESET pin of the target CPU, which is typically called 'nRST', 'nRESET' or 'RESET'. |

Pin 3 is GND pin connected to GND in J-Link. It should also be connected to GND in the target system.

Homemade Spi Flash Programmer Software Download For Mac Windows 10

Notes regarding nRESET: If there is another device / peripheral that also controls the SPI flash (e.g. a CPU the flash is connected to), nRESET of J-Link should be connected to the reset of the target system or the reset pin of the CPU to make sure that J-Link can keep the CPU in reset while programming the SPI flash.

J-Flash SPI connection

J-Flash SPI is able to auto-detect common SPI flashes automatically, via their respective ID. Anyhow, since all flash parameters (size, commands etc.) can also be manually configured by the user, any SPI flash device can be supported. The list of flash devices that are supported by the flash auto-detection of J-Flash SPI can be found here:

Atmel / Adesto DataFlash

Atmel DataFlash is not supported by J-Flash SPI as its instruction set and handling in general is significantly different from any other SPI flash. Moreover, its page/sector size is not a power of 2, making it incompatible to existing concepts.

Hp compaq nx6125 audio drivers for windows 7. Selecting the right (Q)SPI flash that fits the needs can be a difficult task. There are plenty of different flashes as well as vendors available and creating a hardware for each candidate is time consuming and costly.

To make evaluation of different (Q)SPI flashes a lot easier, we have created a (QSPI) evaluation board.

Command line version

A command line version of J-Flash SPI is available for Windows, Linux and macOS, too. The command line version is also part of the J-Link software and documentation package. Please note that the GUI version of J-Flash SPI can also be controlled from the command line.

Due to the high performance and the efficient protocol of J-Link/Flasher, programming speeds up to the max. flash programming specified by the flash vendor, can be achieved.

| Flash device | Programming speed1 |

|---|---|

| ISSI IS25LP128 | 500 KB/s |

| ISSI IS25LD040 | 100 KB/s |

| ISSI IS25LQ080 | 340 KB/s |

| ISSI IS25CD010 | 100 KB/s |

| ISSI IS25CQ032 | 190 KB/s |

| Macronix MX25L3235E | 285 KB/s |

| Macronix MX66L1G45G | 430 KB/s |

| Macronix MX66L51235F | 315 KB/s |

| Micron N25Q128A | 270 KB/s |

| Micron M25P10 | 160 KB/s |

| Micron M25PX16 | 230 KB/s |

| Micron M45PE10 | 230 KB/s |

| Micron M25PE4 | 215 KB/s |

| Spansion S25FL128 | 410 KB/s |

| Spansion S25FL116K | 265 KB/s |

| Winbond W25Q128FV | 340 KB/s |

Homemade Spi Flash Programmer Software Download For Mac Os

1 Max. flash programming speed that can be achieved depends on flash device. Flash programming is done in pages and page size as well as page programming time varies from device to device. For more information about the page programming time for a specific flash device, please refer to the appropriate datasheet.

FAQ

Homemade Spi Flash Programmer Software Download For Mac Download

A: Please check the SEGGER wiki for more information which J-Link hardware versions support the 'SPI interface': wiki.segger.com/Software_and_Hardware_Features_Overview